### Introduction

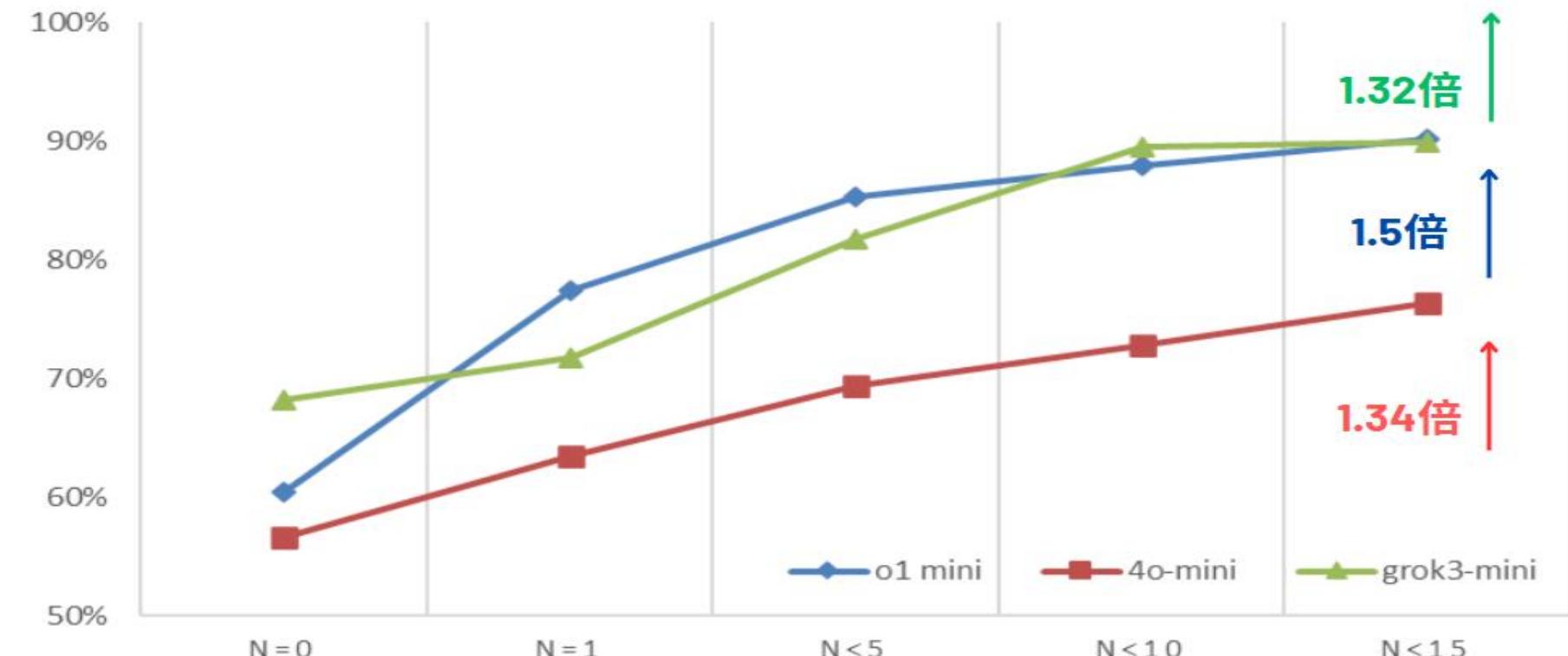

在數位 IC 設計領域中，RTL 的設計和驗證是重要的一環。撰寫硬體描述語言 (HDL) 代碼是一項複雜且耗時的工作，且需要高度的專業。我們透過讓 LLMs 自動迭代生成 Verilog 代碼，結合 EDA 工具進行測試，並且對多達 292 個 Verilog 問題進行分析。在 ChatGPT o1 mini 上，語意正確率提升了 1.5 倍且語法完全正確。說明大語言模型在加速 RTL 設計中的潛力，與此方法可以有效自動修正錯誤代碼的能力。

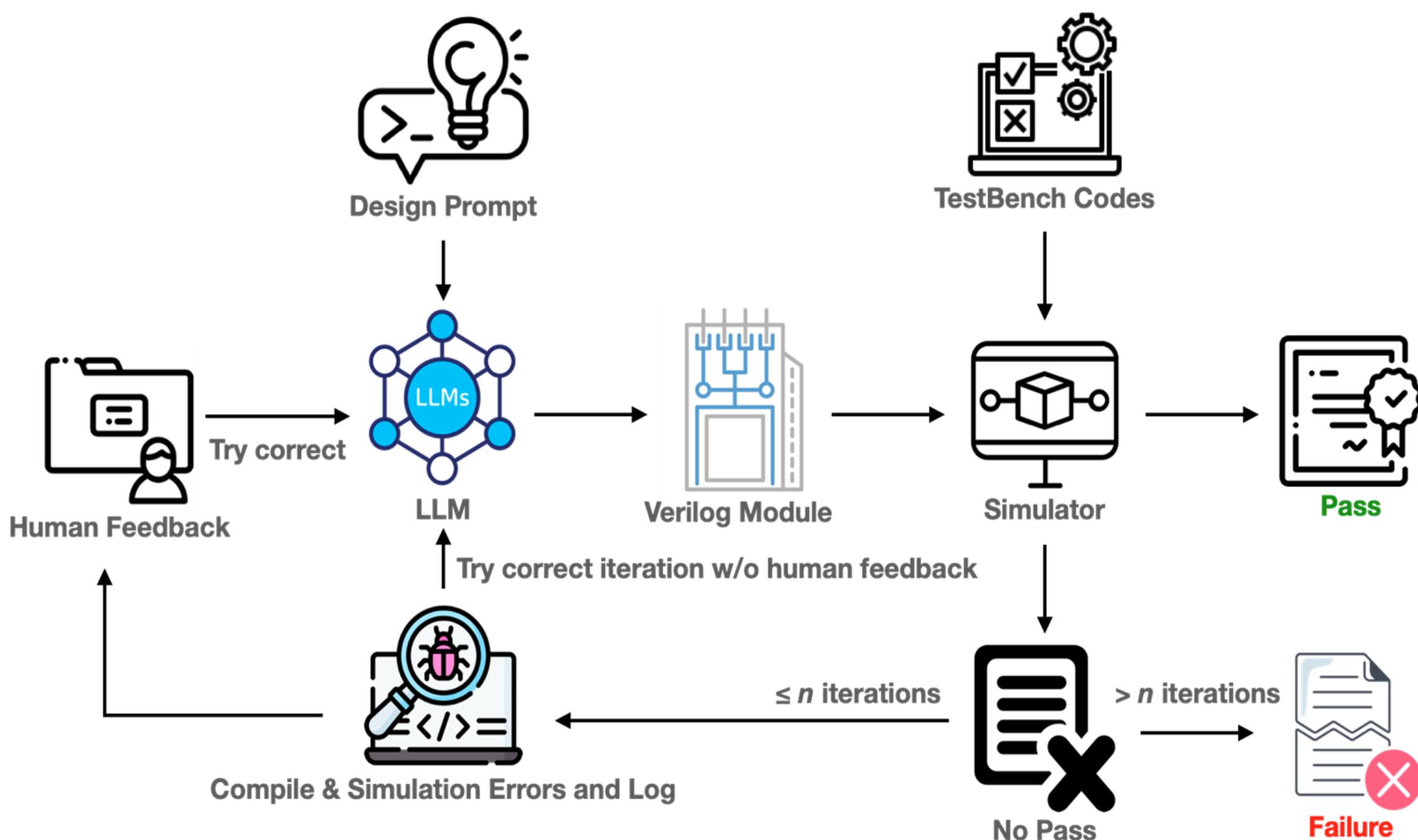

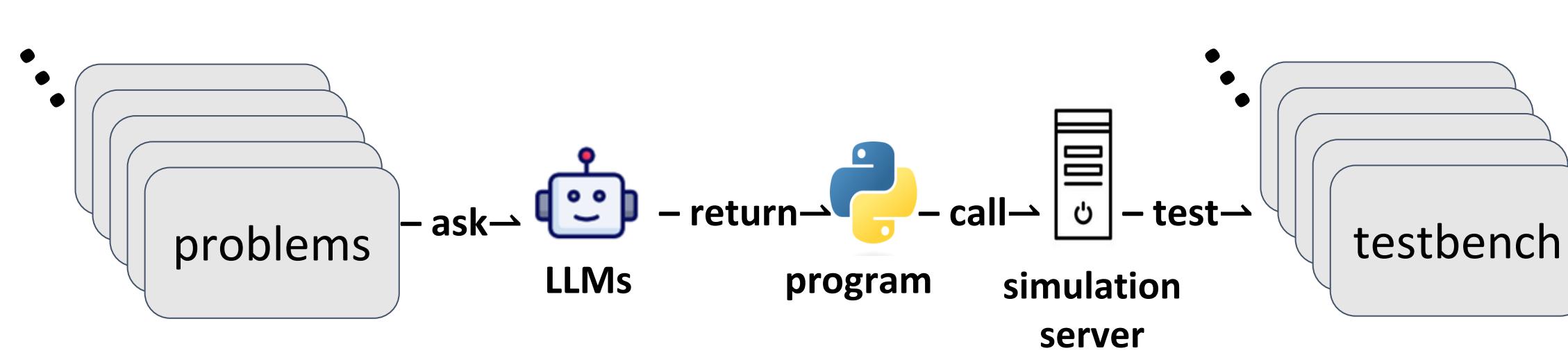

### System Flow

### ChatGPT Success Rate

Table 1

Model Performance on Different Circuit Types

| Circuit Type | 4O     | 4O-MINI | O1-MINI | multimodal |

|--------------|--------|---------|---------|------------|

| CL           | 82.86% | 84.85%  | 94.12%  | 82.35%     |

| SL           | 65.63% | 60.94%  | 67.19%  | 84.00%     |

| BLC          | 83.33% | 57.14%  | 74.13%  | 80.00%     |

Note: Circuit Type - CL (Combinational Logic), SL (Sequential Logic), BLC (Building Larger Circuits).

Table 2

Model Performance on Different Circuit Types

| Difficulty | 4O     | 4O-MINI | O1-MINI | multimodal |

|------------|--------|---------|---------|------------|

| B          | 88.00% | 87.50%  | 87.50%  | 86.36%     |

| Ba         | 85.71% | 71.43%  | 90.48%  | 90.00%     |

| I          | 68.75% | 62.50%  | 75.00%  | 92.31%     |

| H          | 66.67% | 58.33%  | 79.17%  | 70.00%     |

| E          | 47.37% | 50.00%  | 45.00%  | 78.57%     |

Note: Difficulty - B (Beginner), Ba (Basic), I (Intermediate), H (Hard), E (Expert).

SUCCESS RATE WITH N ITERATION

### Design Prompt : 261 Verilog 問題及 Testbench

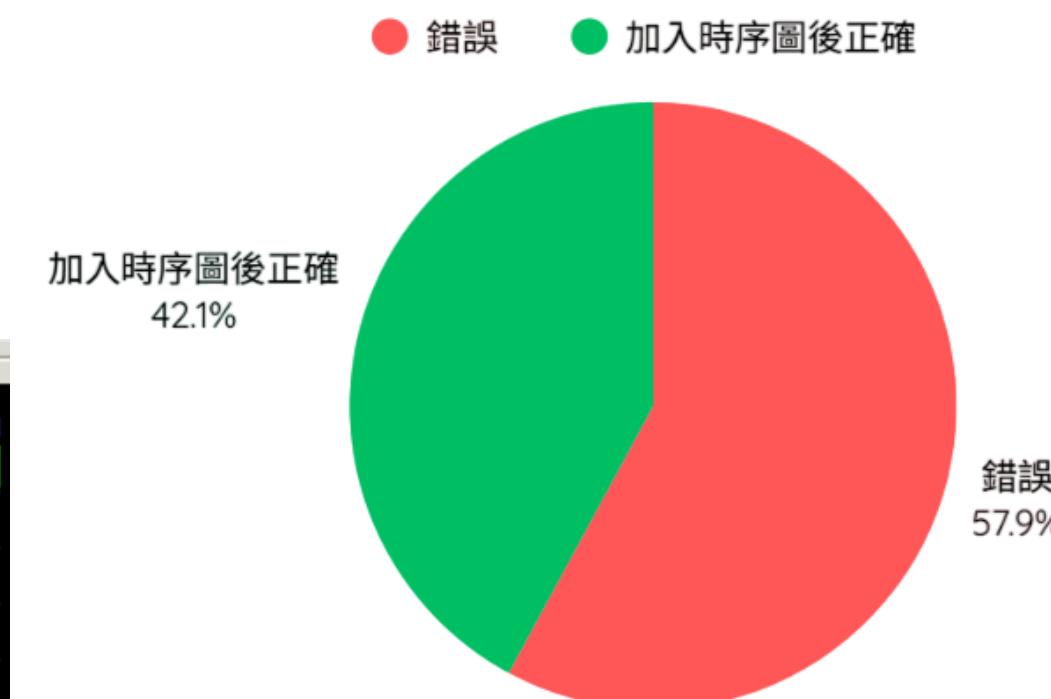

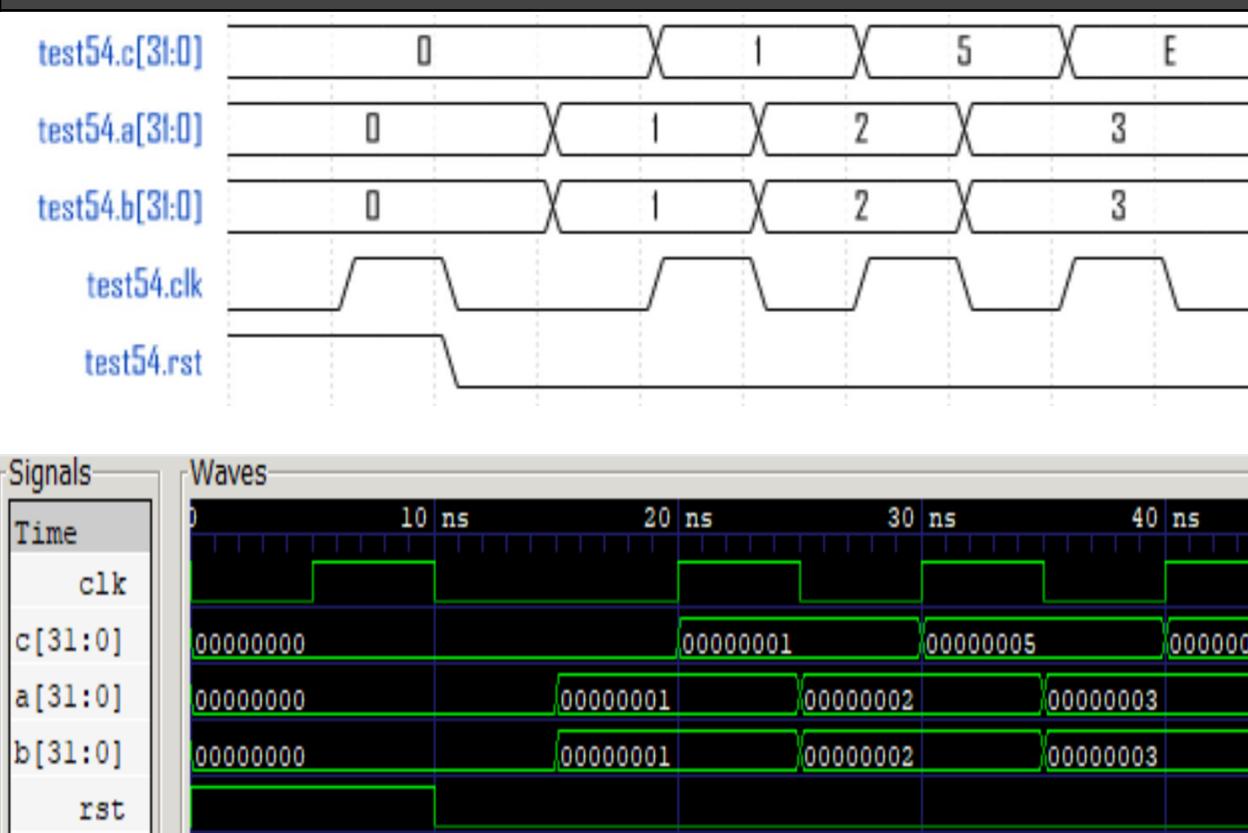

### 時序圖策略 Waveforms

### 系統功能特色

- 錯誤回饋和修正：平台允許使用者看到每次錯誤訊息，並可以對任意次的錯誤進行人為修改與後續迭代

- 使用模型：ChatGPT 4o mini、o1 mini、4、4o、Grok-3 mini

- 難度與種類選擇：三種電路，五種難度

### 結果與討論

- 技術可行性：語法上，得到 100% 的正確率，提升約 1.4 倍；而在語意驗證上有最高 90.19% 的正確率，提升約 1.5 倍，新增時序圖後更提升至 93.21%。

- 資料庫優勢：我們有最多的開源 Verilog 題目資料集且未來將持續擴大到至少 500 題。

- 應用：電類學生，研究開發人員，IC 設計公司。

- 正確率在 15 迭代之間收斂，因此我們將測試限制在 15 次迭代。

- 返回前一次( $n-1$ 次)而非( $n$ 次)的錯誤訊息和代碼給 LLMs 時，可達到更高的成功率。

- 我們正在微調聯發科 Breeze-7B-FC 與 Llama3.2 3B，透過我們大量的資料集，希望能在 Verilog 領域達到大型 LLMs 的正確率。並將目標著重在複雜電路如 8 bit 微處理機的研究。